**Vishay Semiconductors**

# **Circuit Description of the IR Receiver Modules**

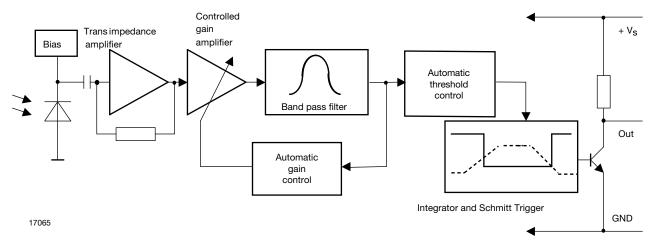

All Vishay IR receivers have the same circuit architecture. The functional block diagram of the Vishay TSOP IR receiver modules can be seen in figure 1. The infrared signal generates an equivalent photo current in the photo PIN diode. The DC part of the signal is blocked in the bias circuit and the AC part is passed to a trans impedance amplifier followed by an automatic gain-control amplifier and an integrated band pass filter. A comparator, an integrator and a Schmitt Trigger stage perform the final signal conditioning. The blocks "Automatic Gain Control" and "Automatic Threshold Control" dynamically control the operating points as well as the threshold levels required to suppress noise from disturbance sources. The digital output signal has an active low polarity and consists of an envelope signal of the incoming optical burst, without the carrier frequency.

Fig. 1 - Simplified Block Diagram of TSOP IR Receivers

#### TRANS IMPEDANCE AMPLIFIER

The Bias block provides the necessary bias voltage for the detector diode and also separates the DC and low frequency components from the useful signal by providing a low impedance path to ground. The AC signals are passed unhindered to the trans impedance amplifier.

The currents at the signal frequency are converted by the trans impedance amplifier to a voltage at the input of the Controlled Gain Amplifier.

## **CONTROLLED GAIN AMPLIFIER**

Most of the gain in the system is generated in the controlled gain amplifier, whereby the degree of amplification is controlled by the Automatic Gain Control (AGC) block. The gain variation of this amplifier is about 45 dB.

#### **BAND PASS FILTER**

The band pass filter is an important system block, required to obtain good performance in disturbed or noisy ambients. The filter attenuates noise coming from various disturbance sources. As the burst duration in some IR remote control data formats is relatively short, the figure of merit or Q cannot be more than 10, as a higher Q band pass filter would need a longer burst time to become oscillating.

| TABLE 1 - BAND PASS FILTER IN THE TSOP RECEIVER: FIGURE OF MERIT |      |        |      |      |      |  |  |

|------------------------------------------------------------------|------|--------|------|------|------|--|--|

|                                                                  | AGC1 | AGC2/8 | AGC3 | AGC4 | AGC5 |  |  |

| Figure of merit (band pass filter)                               | 7    | 10     | 10   | 10   | 10   |  |  |

The band pass filter is tuned during the production process. The following band pass center frequencies are available: 30.3 kHz, 33 kHz, 36 kHz, 36.7 kHz, 38 kHz, 40 kHz, 44 kHz, and 56 kHz. These are the carrier frequencies for the most common data formats of IR remote controls. The duty cycle of the carrier frequency can be between 50 % and 5 %. A remote control system using a Vishay IR receiver is more efficient regarding battery power consumption on the emitter side if the carrier duty cycle is low. This is shown in the following example:

# Vishay Semiconductors Circuit Description of the IR Receiver Modules

- Carrier duty cycle 50 %, peak current of emitter  $I_F$  = 200 mA, the resulting transmission distance is 25 m

- Carrier duty cycle 10 %, peak current of emitter  $I_F = 800$  mA, the resulting transmission distance is 29 m

## **AUTOMATIC GAIN CONTROL (AGC)**

The AGC stage ensures that the receiver module is insensitive to disturbance signals. It adapts the system sensitivity to the existing noise or disturbance level by changing the gain of the amplifier. In dark ambient, the AGC also sets the gain to the most sensitive value at which there are no longer any random output pulses. The time constant of the AGC was chosen to be sufficiently large enough to avoid a decrease in sensitivity during normal transmission. The AGC does not react to the useful signal but reduces the sensitivity in case of disturbances. Hence the AGC has to distinguish between useful and disturbance signals. To achieve this, the AGC needs to distinguish between these good and bad signals. The characteristics used to destinguish the signals are different for the various IR receiver series from Vishay. The criteria used are mainly burst length and envelope duty cycle. In table 2, there are some figures that show the AGC criteria for data signals.

| TABLE 2 - CONDITIONS OF THE AGC FOR DATA SIGNAL                                |                            |                          |                          |                           |        |  |  |  |

|--------------------------------------------------------------------------------|----------------------------|--------------------------|--------------------------|---------------------------|--------|--|--|--|

|                                                                                | AGC1                       | AGC2/8                   | AGC3                     | AGC4                      | AGC5   |  |  |  |

| Maximum burst length for high duty cycle                                       | 1.8 ms                     | 1.8 ms                   | 1 ms                     | 1 ms                      | 0.6 ms |  |  |  |

| Idle time needed for each burst longer than the max. burst length (above line) | 1.2 x time<br>burst length | 4 x time<br>burst length | 6 x time<br>burst length | 10 x time<br>burst length | 25 ms  |  |  |  |

| Maximum number of short bursts in 1 s                                          | 2000                       | 800                      | 2000                     | 1300                      | 2000   |  |  |  |

## **AUTOMATIC THRESHOLD CONTROL (ATC)**

After the band pass filter, the signal is evaluated by a comparator. In quiescent mode (no data signal present), there should be no output signal due to noise, i.e. the threshold of the comparator is set above the noise floor. When a signal is received, the comparator threshold level is adjusted upward to a higher value. This shift prevents random pulses occurring during a data message.

A further benefit of the ATC is the stabilisation of the output pulse width. Without the ATC, the output pulses would vary with the strength of the IR input signals.

The comparator threshold level reverts back to the initial value after a time of approximately 10 ms if it is not retriggered in the meantime. This time constant ensures a stable signal evaluation during the data message for the most common transmission codes. This method efficiently avoids having disturbance pulses being detected as falsely transmitted signals during the transmission of an information block.

## INTEGRATOR AND SCHMITT TRIGGER

The integrator is triggered when the signal reaches the above mentioned comparator threshold. Several consecutive cycles of the carrier signal at the comparator output are required before the integrator finally triggers the output.

The integration time necessary to control the output via the Schmitt Trigger is given in table 3 for each of the IR receiver module series.

The integrator defines a minimum time for the burst length (integrator ramp up time) and a minimum time between the bursts (integrator ramp down time).

The integrator prevents the feed-through of short disturbances or spikes to the output. A long integrator ramp time can improve the signal to noise ratio significantly. The design of the integrator and Schmitt Trigger combination was optimised such that the output pulse width is close to the optical burst length at the input.

| TABLE 3 - INTEGRATOR DATA OF THE VISHAY IR RECEIVER |           |           |           |           |           |  |  |  |

|-----------------------------------------------------|-----------|-----------|-----------|-----------|-----------|--|--|--|

|                                                     | AGC1      | AGC2/8    | AGC3      | AGC4      | AGC5      |  |  |  |

| Minimum burst length                                | 6 cycles  | 10 cycles | 6 cycles  | 10 cycles | 6 cycles  |  |  |  |

| Minimum gap between the bursts                      | 10 cycles | 12 cycles | 10 cycles | 12 cycles | 10 cycles |  |  |  |

## **OUTPUT STAGE**

As shown in figure 1, the digital output of the TSOP IR receiver modules is an open collector transistor with an internal pull up resistor. An additional external pull up resistor can optionally be used if more current is needed to drive the input of the decoding device or if a faster switching time is required. The logic low level will be below 0.2 V even at a sink current of 2 mA. The output can continuously drive a capacitance of up to 1 nF without risk of damaging the

#### output stage.

If is not recommended to pull down the output of the IR receivers to a voltage below 1 V by a pull down resistor or any other external components. Some IR receiver types might not work properly in that condition because a standby mode is activated.